Page 81 - 22-0722 EBOOK

P. 81

วารสารราชบััณฑิิตยสภา

ปีีที่่� ๔๖ ฉบัับัที่่� ๓ กัันยายน-ธัันวาคม ๒๕๖๔

ศาสตราจารย์์กิิตติคุุณ ดร.มงคุล เดชนคุรินทร์ 71

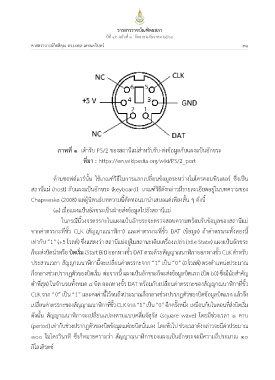

ภาพท่� ๑ เตั้ารับ PS/2 ข้องสถูานี้้แม่สำาหรับรับ-ส่งข้้อมูลกับแผงแป้นี้อักข้ระ

ท่�มูา : https://en.wikipedia.org/wiki/PS/2_port

ด้านี้ซอฟตั์แวร์นี้ั�นี้ ใช้้เกณฑ์์วิธี้ในี้การแลกเปล้�ยนี้ข้้อมูลระหว่างไมโครคอมพิิวเตัอร์ ซ่�งเป็นี้

สถูานี้้แม่ (host) กับแผงแป้นี้อักข้ระ (keyboard) เกณฑ์์วิธี้ดังกล่าวม้รายละเอ้ยดอยู่ในี้บทความข้อง

Chapweske (2008) แตั่ผู้นี้ิพินี้ธี์บทความนี้้�ตััดทอนี้มานี้ำาเสนี้อแตั่เพิ้ยงสั�นี้ ๆ ดังนี้้�

(๑) เม่�อแผงแป้นี้อักข้ระเป็นี้ฝ่่ายส่งข้้อมูลไปยังสถูานี้้แม่

ในี้กรณ้นี้้�วงจรตัรรกะในี้แผงแป้นี้อักข้ระจะตัรวจสอบความพิร้อมรับข้้อมูลข้องสถูานี้้แม่

จากค่าตัรรกะท้�ข้ั�ว CLK (สัญญาณนี้าฬิิกา) และค่าตัรรกะท้�ข้ั�ว DAT (ข้้อมูล) ถู้าค่าตัรรกะทั�งสองนี้้�

เท่ากับ “1” (+5 โวลตั์) ซ่�งแสดงว่า สถูานี้้แม่อยู่ในี้สถูานี้ะเดินี้เคร่�องเปล่า (Idle State) แผงแป้นี้อักข้ระ

ก็จะส่งบิตันี้ำาหร่อ บิตเริ�มู (Start Bit) ออกทางข้ั�ว DAT ตัามด้วยสัญญาณนี้าฬิิกาออกทางข้ั�ว CLK สำาหรับ

ประสานี้เวลา สัญญาณนี้าฬิิกานี้้�จะเปล้�ยนี้ค่าตัรรกะจาก “1” เป็นี้ “0” (0 โวลตั์) ตัรงตัำาแหนี้่งประมาณ

ก่�งกลางช้่วงปรากฏตััวข้องบิตัเริ�ม ตั่อจากนี้้� แผงแป้นี้อักข้ระก็จะส่งข้้อมูลบิตัแรก (บิตั b0) ซ่�งม้นี้ัยสำาคัญ

ตัำ�าท้�สุด) ในี้จำานี้วนี้ทั�งหมด ๘ บิตั ออกทางข้ั�ว DAT พิร้อมกับเปล้�ยนี้ค่าตัรรกะข้องสัญญาณนี้าฬิิกาท้�ข้ั�ว

CLK จาก “0” เป็นี้ “1” และคงค่านี้้�ไว้จนี้ถู่งประมาณก่�งกลางช้่วงปรากฏตััวข้องบิตัข้้อมูลบิตัแรก แล้วจ่ง

เปล้�ยนี้ค่าตัรรกะข้องสัญญาณนี้าฬิิกาท้�ข้ั�ว CLK จาก “1” เป็นี้ “0” อ้กครั�งหนี้่�ง เหม่อนี้กับในี้ตัอนี้ท้�ส่งบิตัเริ�ม

ดังนี้ั�นี้ สัญญาณนี้าฬิิกาจะเปล้�ยนี้แปลงตัามแบบคล่�นี้จัตัุรัส (square wave) โดยม้ช้่วงเวลา ๑ คาบ

(period) เท่ากับช้่วงปรากฏตััวข้องบิตัข้้อมูลแตั่ละบิตันี้ั�นี้เอง โดยทั�วไป ช้่วงเวลาดังกล่าวจะม้ค่าประมาณ

๑๐๐ ไมโครวินี้าท้ ซ่�งก็หมายความว่า สัญญาณนี้าฬิิกาข้องแผงแป้นี้อักข้ระจะม้ความถู้�ประมาณ ๑๐

กิโลเฮิรตัซ์